DTCO Device Lab, PKU

The Power of Nature is Unbelievable

Heng Wu, Associate professor at the School of Integrated Circuits of Peking University from 2023.

Experiences: Research Staff Member at IBM T. J. Watson Research Center in New York State, USA from 2016 to 2022, working towards Next-gen Logic Development. Prior to this, I received the Ph.D. degree in Electrical and Computer Engineering from Purdue University under Professor P.D. Ye in 2016, with a thesis on Beyond Si CMOS.

Research: My research focuses on Design Technology Co-optimization (DTCO), 3D Integration, VLSI Device&Design and Semiconductor Devices&Physics. I have published more than 80 papers/book chapters and filed more than 500 US/China/EU patents.

Recognitions: Recipient of Best Paper Awards of several renowned conferences such as VLSI2024, DRC2015, TECHON2015 and SISC2013. I also received the IEEE Paul Rappaport Award and was appointed as “IBM Master Inventor”.

Openings: The group has openings for potential graduate students and post-doc researchers. If you are interested in pioneering/contributing in advancement of IC technology, This is the place.

Expectation for Potential Students: Problem-solving,Team-working and Enthusiasm. You are strongly encouraged to read two textbooks: < Fundamentals of Modern VLSI Devices> by Tak H. Ning & Yuan Taur and < Digital Integrated Circuits, A Design Perspective> by Jan. Rabaey.

THINK, THINK DIFFERENT and HARD WORKING.

If you want to be successful, attitude is everything. We have all the knowledge you need and you ought to be ready to have the attitude to do something with it.

—Robert H. Dennard —

news

selected publications

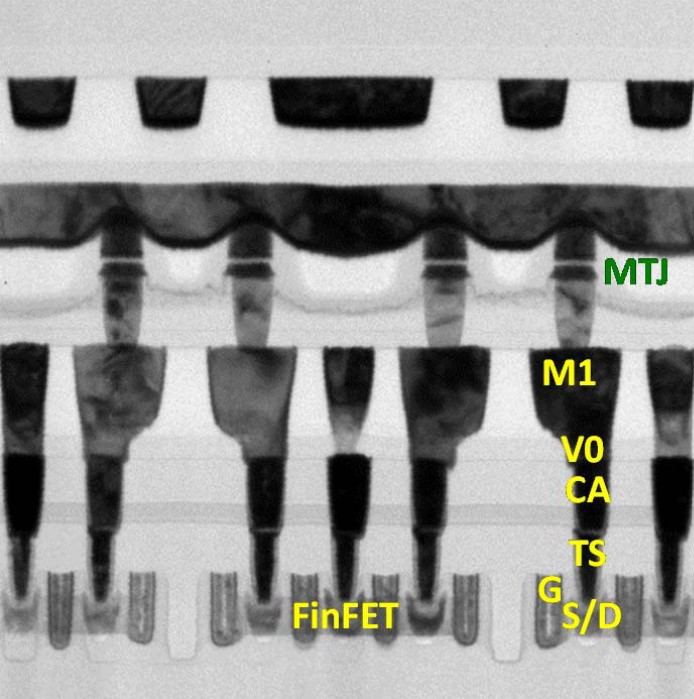

- IEDM

A 14 nm embedded stt-mram cmos technologyIn 2020 IEEE International Electron Devices Meeting (IEDM), 2020

A 14 nm embedded stt-mram cmos technologyIn 2020 IEEE International Electron Devices Meeting (IEDM), 2020